# Modeling of Picosecond Pulse Propagation in Microstrip Interconnections on Integrated Circuits

KEITH W. GOOSSEN, MEMBER, IEEE, AND ROBERT B. HAMMOND, MEMBER, IEEE

**Abstract** — We have made theoretical time-domain analyses of the dispersion and loss of square-wave and exponential pulses on microstrip transmission line interconnections on silicon integrated-circuit substrates, using the quasi-TEM approximation. Geometric dispersion and conductor line width, as well as losses from conductor resistance, conductor skin effect, and substrate conductance, are considered over the frequency range from 100 MHz to 100 GHz. Results show the enormous significance of the substrate losses and demonstrate the need for substrate resistivities  $> 10 \Omega \cdot \text{cm}$  for high-performance circuits. The results also show the effects of geometric dispersion for frequencies above 10 GHz (which increase with decreasing line width), the unimportance of conductor skin-effect losses for frequencies up to 100 GHz, and the transition from a high-frequency regime where losses do not affect phase velocity to a low-frequency regime where the ratio of the conductor and substrate loss coefficients determines phase velocity. Qualitatively similar phenomena are seen for Al, W, and  $\text{WSi}_2$  lines, but low-frequency velocity is increased for either increasing conductor resistivity, decreasing conductor line width, or both. Poly-Si, with its significantly greater loss, shows qualitatively different frequency-dependent behavior. High phase velocity and high loss can coexist in poly-Si lines.

## I. INTRODUCTION

BECAUSE OF the increasing speed of very large scale integrated circuitry (VLSI) and the development of very high speed integrated circuits (VHSIC's), knowledge of pulse dispersion and loss in the subnanosecond regime is becoming important to the Si integrated-circuit designer. Ultimate device switching speeds for both field-effect transistor (FET) and bipolar transistor technologies have been projected into the few ps regime [1]; however, if future high-speed circuits are to take advantage of even the switching speeds already demonstrated in both FET (30 ps) [2] and bipolar (30 ps) [3] Si IC's, limitations due to the device interconnections must be addressed. Hasegawa and Seki [4] have shown that the common circuit design approach of using lumped-capacitance models for inter-

Manuscript received December 21, 1987; revised August 23, 1988. This work was done under internal supporting research at the Los Alamos National Laboratory, which is operated by the University of California for the United States Department of Energy under Contract W-7405-ENG-36. The first author acknowledges the U.S. Department of Energy Magnetic Fusion Energy Technology Fellowship Program.

K. W. Goossen was with the Electronics Division, Los Alamos National Laboratory, Los Alamos, NM 87545. He is now with AT&T Bell Laboratories, Crawfords Corner Rd., Holmdel, NJ 07733.

R. B. Hammond was with the Electronics Division, Los Alamos National Laboratory, Los Alamos, NM 87545. He is now with Superconducting Technologies, Inc., Santa Barbara, CA.

IEEE Log Number 8825380.

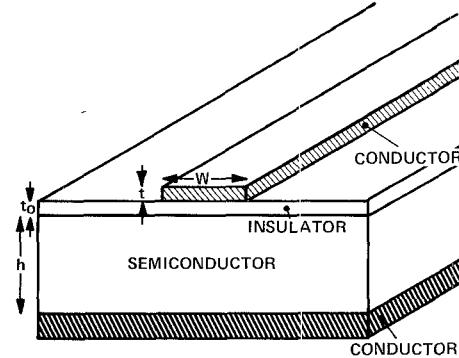

Fig. 1. Microstrip transmission line on Si substrate.

connections is not adequate when switching speeds are  $< 100 \text{ ps}$ . The lumped-capacitance model assumes that pulse rise times are much greater than signal propagation delays, but this assumption is not valid for high-speed VLSI circuits. Reflections at discontinuities, inductive effects such as slow wave, substrate losses, conductor losses, and geometric dispersion are all important. The microstrip transmission line offers a metal interconnection structure with excellent high-frequency properties that is easily incorporated into Si IC's; in addition, the quasi-TEM analysis of this structure is valid to switching speeds of 7 ps. Although the isolated microstrip transmission line does not completely characterize the integrated circuit interconnection embedded in a complex circuit environment, a thorough understanding of the isolated line is a first step to developing useful high-frequency models for real device interconnections.

In this paper, we present theoretical results for pulse propagation on microstrip transmission lines on Si IC substrates (Fig. 1). Our analyses use equations for the effective dielectric constant, conductor loss, skin-effect loss, and dielectric loss, which are derived in the cited references. We assumed quasi-TEM-mode propagation throughout the analysis. Since a static analysis would be valid only for low frequency, we included a number of frequency-dependent effects that occur at high frequencies. The lowest order effects of high frequencies can be included in the quasi-TEM analysis by including the frequency dependences of both the effective dielectric con-

stant and the losses. The line is dispersive because the propagation factor of the transmission line has a nonlinear variation with  $w$ . This effect is caused by geometric dispersion in the microstrip line (reflected in the frequency dependence of the effective dielectric constant), by the finite conductivity of the Si substrate, and by the finite value, as well as the frequency dependence (due to skin effect), of the resistance of the metal conductor. We included all these effects in a computer model and performed time-domain analyses of pulse propagation on Si substrates. The analyses are valid for frequencies up to the lowest frequency where non-TEM modes can propagate in the microstrip interconnections, i.e., the cutoff frequency for the surface wave mode [5]. This cutoff frequency is inversely related to the substrate thickness and is 50 GHz for a Si wafer thickness of 450  $\mu\text{m}$ . (A bandwidth of 50 GHz corresponds to a pulse rise time of 7 ps in a linear, single-time-constant system.)

We attempted to choose microstrip parameters and input waveforms that are relevant to current and future Si integrated-circuit technology. Substrate resistivities of 10 and 100  $\Omega \cdot \text{cm}$  were chosen because 10  $\Omega \cdot \text{cm}$  is the most common resistivity used for high-performance Si IC's and 100  $\Omega \cdot \text{cm}$  offers great reductions in line losses and may well be used in the future for higher performance circuitry. We chose 450  $\mu\text{m}$  wafer thickness, a 0.5  $\mu\text{m}$  conductor thickness, and a 1  $\mu\text{m}$  field oxide thickness because they are typical values used in real circuits. We chose aluminum, tungsten, tungsten silicide, and poly-Si as center conductor materials because they cover the full range of resistivities of materials used as interconnections in high-performance Si IC's. We used conductor line widths of 10 and 300  $\mu\text{m}$  because 10  $\mu\text{m}$  is a typical conductor width on high-performance IC's and 300  $\mu\text{m}$  has a characteristic impedance of 50  $\Omega$  and thus might be used for high-frequency output lines.

With these substrate resistivities, and in the frequency range used ( $< 100$  GHz), we avoid the "slow-wave" and "skin-effect" modes as described by Hasegawa [6]. Even so, a low-frequency regime is found to exist *within the quasi-TEM approximation*, where losses play a more prominent role in determining phase velocity. The phase velocity in this regime is shown to depend on the ratio of the conductor and substrate loss coefficients, in such a way that when this ratio is unity, the phase velocity is maximized to the value of the phase velocity when there are no losses. Thus even when losses are high, large velocities may be achieved by balancing the losses in the conductor and in the substrate.

We examined the effects of interconnection dispersion and losses on high-speed logiclike pulses. We used 50 ps square-wave pulses with 12 ps rise and fall times for the input pulse waveforms in our calculations. We present time-domain plots of the initial pulses and plots of the same pulses after propagation lengths of 1.5 to 6.0 mm. Also, for some cases, we considered pulses of the form

$$V(t) = \exp(-t/\tau_1)[1 - \exp(-t/\tau_2)]. \quad (1)$$

This waveform approximates the pulse produced by radiation-damaged Si photoconductors, which are of interest because they can be used to perform time-domain studies of high-speed pulse-propagation phenomena on Si IC's [7].

## II. ANALYSIS

The problem is to find  $V(z, t)$ , the voltage waveform at a position  $z$  on the microstrip line, given  $V(0, t)$ , the voltage waveform at the origin. This is accomplished by Fourier decomposing  $V(0, t)$ , multiplying by the propagation factor, and then taking the inverse transform. That is,

$$V(z, t) = F^{-1}\{\exp[-(\alpha + j\beta)z] * F[V(0, t)]\} \quad (2)$$

where  $F$  and  $F^{-1}$  denote the forward and inverse Fourier transforms and  $\alpha$  and  $\beta$  are the attenuation and propagation constants. A frequency-domain mesh of 100 MHz is used, since the bandwidth we consider is 1–100 GHz.

We assume that the substrate's dielectric constant,  $\epsilon_r$ , is real and constant. (This assumption is valid in Si up to  $10^{13}$  Hz.) At 100 MHz, the capacitance introduced by the insulator is a negligible impedance as long as  $t_0 \ll h$  (Fig. 1), as it is in our examples. Therefore, we incorporate the effect of the oxide layer by treating it as an open circuit at zero frequency and as a short circuit at all other frequencies.

As mentioned, quasi-TEM propagation is assumed in this analysis. This has been justified by Hasegawa [6] for the substrate resistivities and frequencies used in our examples. Conductor resistivity introduces limitations to the validity of the quasi-TEM approximation. Here we examine these limitations by finding the ratio of the longitudinal and tangential electric fields of the mode. If this ratio is much smaller than one, the quasi-TEM approximation is justified. Because we are interested in the order of magnitude of this ratio, we calculate it using a parallel-plate model. We find that

$$\frac{|E_z|}{|E_x|} = \frac{1}{\sigma\delta} \frac{2\epsilon_0\epsilon_r}{\mu_0}, \quad t \gg \delta \quad (3a)$$

$$\frac{|E_z|}{|E_x|} = \frac{1}{\sigma t} \frac{\epsilon_0\epsilon_r}{\mu_0}, \quad t \ll \delta \quad (3b)$$

where  $\sigma$  is the conductivity of the conductor,  $\delta$  is the skin depth in the conductor, and  $t$  is its thickness. This ratio is much smaller than 1 for all our examples and is largest for the 0.5  $\mu\text{m}$ -thick poly-Si line, where it is 0.1 at frequencies below 10<sup>12</sup> Hz (the skin depth in poly-Si is about 1  $\mu\text{m}$  at 10<sup>12</sup> Hz, assuming a resistivity of 500  $\mu\Omega \cdot \text{cm}$ ).

The effective dielectric constant,  $\epsilon_{\text{eff}}$ , and the characteristic impedance,  $Z_0$ , at zero frequency have been calculated by Schneider [8] (Fig. 1):

$$\epsilon_{\text{eff}} = [(\epsilon_r + 1) + (\epsilon_r - 1)/\sqrt{1 + 10h/w}]/2 \quad (4)$$

$$Z_0 = 60 \log_e [8h/w + w/(4h)]/\sqrt{\epsilon_{\text{eff}}}, \quad w < h$$

$$= 120\pi/\left\{\left[w/h + 2.42 - 0.44h/w + (1 - h/w)^6\right]\sqrt{\epsilon_{\text{eff}}}\right\},$$

$$w > h. \quad (5)$$

The maximum relative error in these expressions is less than 2 percent, but corrections [9] should be made for  $t/h > 0.005$ .

At high frequencies,  $\epsilon_{\text{eff}}$  must be corrected. Yamashita *et al.* [10] have derived an expression by curve-fitting to a full-wave analysis:

$$\sqrt{\epsilon_{\text{eff}}(f)} = \sqrt{\epsilon_{\text{eff}}(0)} + [\sqrt{\epsilon_r} - \sqrt{\epsilon_{\text{eff}}(0)}] / (1 + 4F^{-3/2}) \quad (6a)$$

where

$$F \equiv 4fh\sqrt{(\epsilon_r - 1)} * \{1/2 + [1 + 2\log_{10}(1 + w/h)]^2\} / c. \quad (6b)$$

Here,  $f$  is the frequency and  $c$  is the speed of light in vacuum. This formula is accurate to approximately 1 percent.

If the material is lossless, the propagation factor  $\beta_0$  is given by

$$\beta_0 = 2\pi f \sqrt{\epsilon_{\text{eff}}} / c. \quad (7)$$

However, finite resistivity of the conductor and finite conductivity of the substrate introduce attenuation. For low frequencies, the conductor loss factor  $\alpha_c$  is given by

$$\alpha_c = \rho_c / (2wtZ_0) \quad (8)$$

in nepers. Here  $\rho_c$  is the resistivity of the metal. This expression, however, assumes a uniform distribution of current in the conductor. At higher frequencies, in the skin-effect regime, the current is not distributed evenly. Pucel *et al.* [11] have formulated the conductor loss in this regime:

$$\begin{aligned} \alpha_c &= [R_s / (2\pi Z_0 h)] * \{1 - [w' / (4h)]^2\} \\ &\quad * \{1 + (h/w') + h[\log_e(4\pi w/t) + t/w] / (\pi w')\}, \\ &\quad w/h < 1/2\pi \end{aligned} \quad (9a)$$

$$\begin{aligned} &= [R_s / (2\pi Z_0 h)] * \{1 - [w' / (4h)]^2\} \\ &\quad * \{1 + (h/w') + h[\log_e(2h/t) - t/h] / (\pi w')\}, \\ &\quad 1/2\pi < w/h < 2 \end{aligned} \quad (9b)$$

$$\begin{aligned} &= [R_s / (Z_0 h)] \\ &\quad / \{w'/h + 2\log_e[2\pi e(w'/2h + 0.94)]/\pi\} \\ &\quad * \{w'/h + [w' / (\pi h)] / [w' / (2h) + 0.94]\} \\ &\quad * \{1 + (h/w') + h[\log_e(2h/t) - t/h] / (\pi w')\}, \\ &\quad 2 < w/h \end{aligned} \quad (9c)$$

where

$$w' \equiv w + t[\log_e(4\pi w/t) + 1] / \pi, \quad w/h < 1/2\pi \quad (9d)$$

$$\equiv w + t[\log_e(2h/t) + 1] / \pi, \quad 1/2\pi < w/h \quad (9e)$$

and

$$R_s \equiv \sqrt{(\pi f \mu \rho_c)}. \quad (9f)$$

Here  $\mu$  is the permeability of the metal. In practice, the conductor loss expression for uniform current distribution

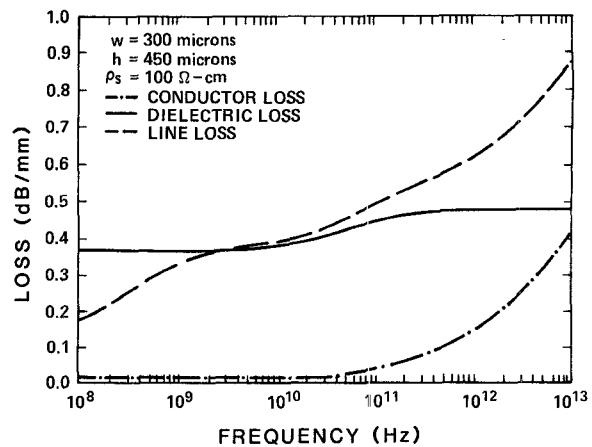

Fig. 2. Conductor loss, dielectric loss, and line loss for a  $50 \Omega$ ,  $0.5\text{-}\mu\text{m}$ -thick Al microstrip line on a  $450\text{-}\mu\text{m}$ -thick,  $100 \Omega\text{-cm}$  Si wafer.

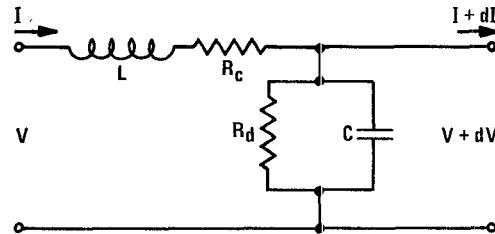

$$\begin{aligned} \frac{dV}{dz} &= -L \frac{dI}{dt} - R_c I \\ \frac{dI}{dz} &= -C \frac{dV}{dt} - \frac{V}{R_d} \\ V, I &\propto e^{(\alpha + i\beta)Z} e^{i\omega t} \end{aligned}$$

Fig. 3. Circuit diagram and circuit equations for the transmission line model used.  $L$  and  $C$  are inductance and capacitance per unit length for the lossless line.  $R_c$  and  $R_d$  are the resistance per unit length introduced by conductor resistance and substrate conductivity.

yields a higher value of attenuation at low frequencies and a lower value at high frequencies than does the expression for skin-effect loss. For our analyses the expression used for  $\alpha_c$  was the one that yielded the higher attenuation at any given frequency (Fig. 2, conduction loss curve).

An expression for dielectric loss  $\alpha_d$  due to nonzero conductivity in the substrate has been derived by Welch and Pratt [12]. Here,  $\sigma_s$  is the conductivity of the substrate:

$$\alpha_d = 60\pi\sigma_s(\epsilon_{\text{eff}} - 1) / [(\epsilon_r - 1)\sqrt{\epsilon_{\text{eff}}}] \quad (10)$$

We now have formulas for  $\beta_0$ , the lossless propagation constant, and  $\alpha_c$  and  $\alpha_d$ , the conductor and dielectric loss constants under *low-loss* conditions (i.e.,  $\alpha_c, \alpha_d, \ll \beta_0$ ). We shall now find expressions for  $\alpha$  and  $\beta$ , the general attenuation and propagation constants, in terms of  $\alpha_c, \alpha_d$ , and  $\beta_0$ . First, we use the circuit model in Fig. 3 and analyze it for general loss conditions. We obtain

$$\alpha^2 = (-f_1 + \sqrt{f_2})/2 \quad (11a)$$

$$\beta^2 = (f_1 + \sqrt{f_2})/2 \quad (11b)$$

where

$$f_1 \equiv w^2 LC - R_c/R_d \quad (12a)$$

$$f_2 \equiv [w^2 LC + (R_c/Z_0)^2][w^2 LC + (Z_0/R_d)^2] \quad (12b)$$

with

$$Z_0 \equiv (L/C)^{0.5}. \quad (12c)$$

Now, if we analyze the circuit model of Fig. 3 for low-loss conditions, we find

$$\alpha_c = R_c/2Z_0 \quad (13a)$$

$$\alpha_d = Z_0/2R_d \quad (13b)$$

$$\beta_0 = \omega\sqrt{LC}. \quad (13c)$$

If we now use these formulas as definitions of the circuit elements ( $R_c$ ,  $R_d$ ,  $L$ ,  $C$ ) in terms of  $\alpha_c$ ,  $\alpha_d$ , and  $\beta_0$ , we rewrite  $f_1$  and  $f_2$ :

$$f_1 = \beta_0^2 - 4\alpha_c\alpha_d \quad (14a)$$

$$f_2 = (\beta_0^2 + 4\alpha_c^2)(\beta_0^2 + 4\alpha_d^2) \\ = [w^2 LC + R^2(C/L)][w^2 LC + G^2(L/C)]. \quad (14b)$$

Since the formulas in (7)–(10) are for conductor and dielectric loss, and propagation factor, in low-loss conditions, we can now substitute these into (11a) and (11b) to obtain  $\alpha$  and  $\beta$  for all loss conditions. In effect, we are deriving the circuit elements in Fig. 3 in terms of (7)–(10).

Our model may be thought of as an extension of the low-loss formulation to lower frequencies. At frequencies above 200 GHz, even the most lossy line we consider (poly-Si conductor on 10  $\Omega\cdot\text{cm}$  substrate) is in the low-loss regime (i.e.,  $\beta_0 \gg \alpha_c, \alpha_d$ ). This can be seen in Fig. 7, since above 200 GHz the phase velocity is independent of loss. By extrapolating to lower frequencies, our model essentially assumes that the circuit elements of the transmission line are independent of frequency (except for the skin-effect dependence of  $R_c$  and the dependence of  $LC$  on frequency as shown in (6)). This assumption is valid as long as we are in the quasi-TEM regime, since a change in field structure would be required to change the circuit elements. Note, however, that since the change of  $LC$  with frequency results from a slight change in field structure within the quasi-TEM formulation, a corresponding change in  $R_c$  and  $R_d$  would be expected. It can be seen in Fig. 5 that this change in field structure is small, so that our model should be little affected.

If  $\alpha_c$  and  $\alpha_d$  are small compared to  $\beta_0$ , then  $\alpha$  and  $\beta$  are given by

$$\alpha = \alpha_c + \alpha_d \quad (15a)$$

$$\beta = \sqrt{(\alpha_c - \alpha_d)^2 + \beta_0^2}. \quad (15b)$$

Fig. 2 illustrates a case where this approximation is valid, but not below 5 GHz.

### III. TRANSFORMED INPUT WAVEFORMS

As stated previously, the voltage response at distance  $z$  down the line is calculated by obtaining the Fourier transform of the input waveform (at  $z = 0$ ), multiplying this by

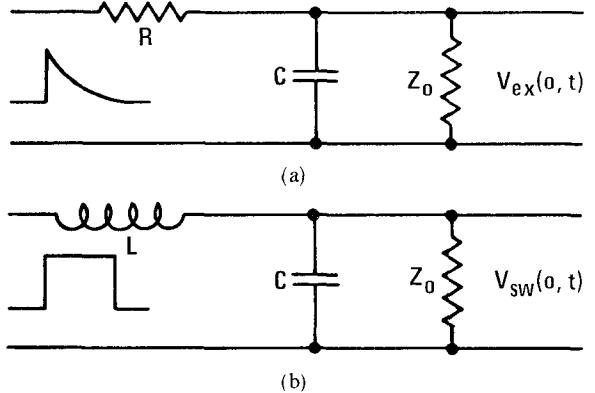

Fig. 4. Circuit diagrams and input pulses used to produce the input waveforms for our model calculations. (a) Circuit for producing exponential waveform: the input pulse is a single exponential function. (b) Circuit for producing square pulse waveform: the input pulse is a perfect square pulse.

the propagation factor ( $\exp[(\alpha + j\beta)z]$ ), and then taking the inverse Fourier transform. The two input waveforms analyzed are square-wave and exponential pulses. To obtain pulses with finite rise and fall times, we applied ideal square-wave and exponential pulses to the circuits in Fig. 4, and we assumed the outputs of the circuits to be the input waveforms for the line. Thus the Fourier transforms of the input signals are given by

$$V_{ex}(0, f) = [1/(j\omega + 1/\tau_1)] * [1/(j\omega\tau_2 + \tau_2/\tau_1 + 1)] \quad (16)$$

where  $\tau_1 = Z_0C$  and  $\tau_2 = RC$ , and

$$V_{sw}(0, f) = [(1 - e^{-j\omega\tau_1})/j\omega] * [1/(-\omega^2/\omega_1^2 + j\omega\tau_2 + 1)] \quad (17)$$

where  $\omega_1^2 = 1/LC$  and  $\tau_2 = L/Z_0$ . By varying the circuit parameters, a variety of pulses can be obtained. After the Fourier transform of the input signal has been multiplied by the frequency-dependent propagation factor, the result is fed into an array at discrete frequencies and a fast Fourier transform routine calculates  $V(z, t)$ .

### IV. RESULTS

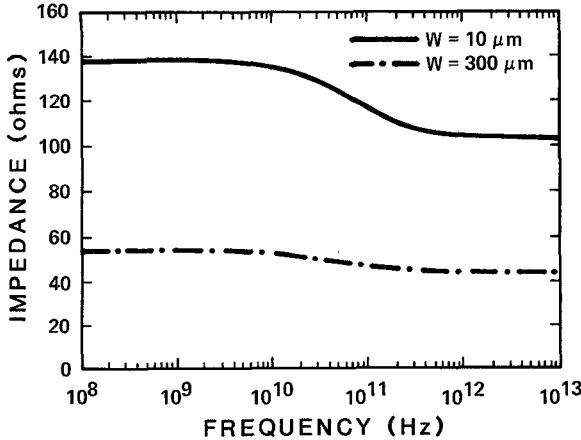

Figs. 5 through 12 show the results of our model calculations. Fig. 5 gives the values for  $Z_0$  versus frequency for both conductor line widths considered (10 and 300  $\mu\text{m}$ ). The plots show clearly the region of geometric dispersion (10 to 300 GHz) for a microstrip line on a 450- $\mu\text{m}$ -thick Si wafer. Also, geometric dispersion is obviously a larger effect for the narrow line width (10  $\mu\text{m}$ ).

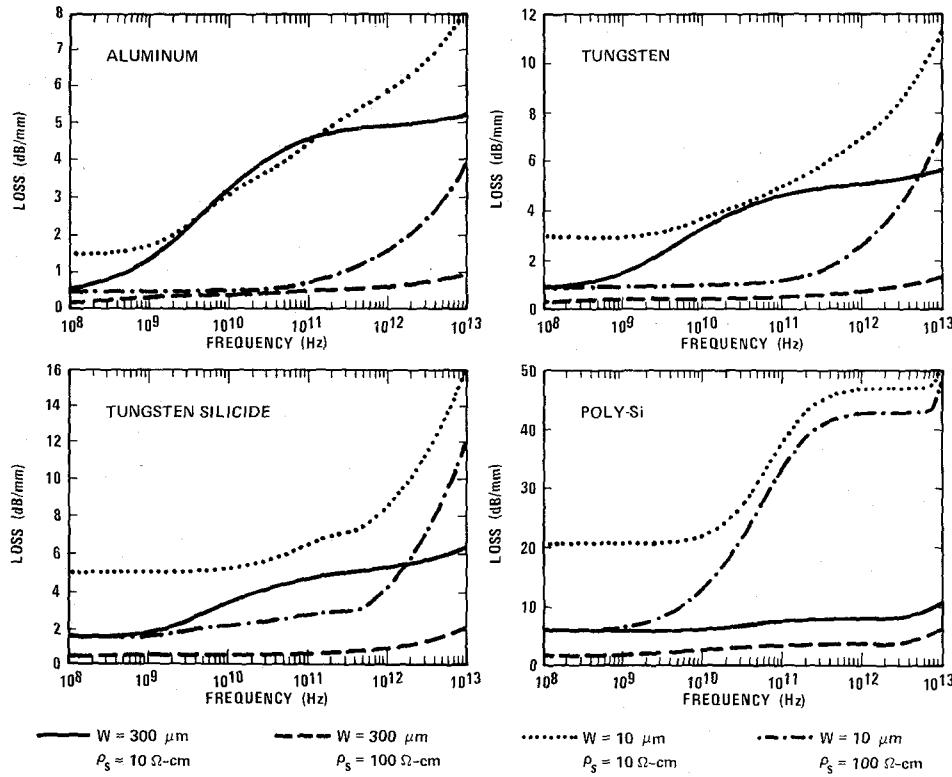

Fig. 6 shows the loss versus frequency for Al (2.7  $\mu\Omega\cdot\text{cm}$ ), W (10  $\mu\Omega\cdot\text{cm}$ ), WSi<sub>2</sub> (30  $\mu\Omega\cdot\text{cm}$ ), and poly-Si (500  $\mu\Omega\cdot\text{cm}$ ) lines of 10 and 300  $\mu\text{m}$  width on 10 and 100  $\Omega\cdot\text{cm}$  substrates. As expected, the losses show monotonic increases with increasing conductor resistivity; however, the

Fig. 5. Characteristic impedance versus frequency for microstrip lines on 450- $\mu\text{m}$ -thick Si wafers for both conductor line widths considered.

increases in loss are not directly proportional to the increases in resistivity. The frequencies at which skin effect becomes the dominant loss (100 GHz for Al, 200 GHz for W, 500 GHz for WSi<sub>2</sub>, and 5 THz for poly-Si) are higher as the material becomes more resistive. However, because frequencies above 50 GHz are too high to be of interest for Si integrated circuits in the near future, skin-effect losses are not important for this analysis. The most significant effect shown is that substrate losses obviously dominate over conductor losses for Al, W, and WSi<sub>2</sub> lines on 10  $\Omega\cdot\text{cm}$  material. Also, for 100  $\Omega\cdot\text{cm}$  substrates, conductor loss goes from being unimportant for Al and W lines to being comparable to substrate loss for WSi<sub>2</sub> lines. Only for the 10- $\mu\text{m}$ -wide poly-Si lines does the conductor loss obviously dominate over substrate loss for both 10 and 100  $\Omega\cdot\text{cm}$  substrates.

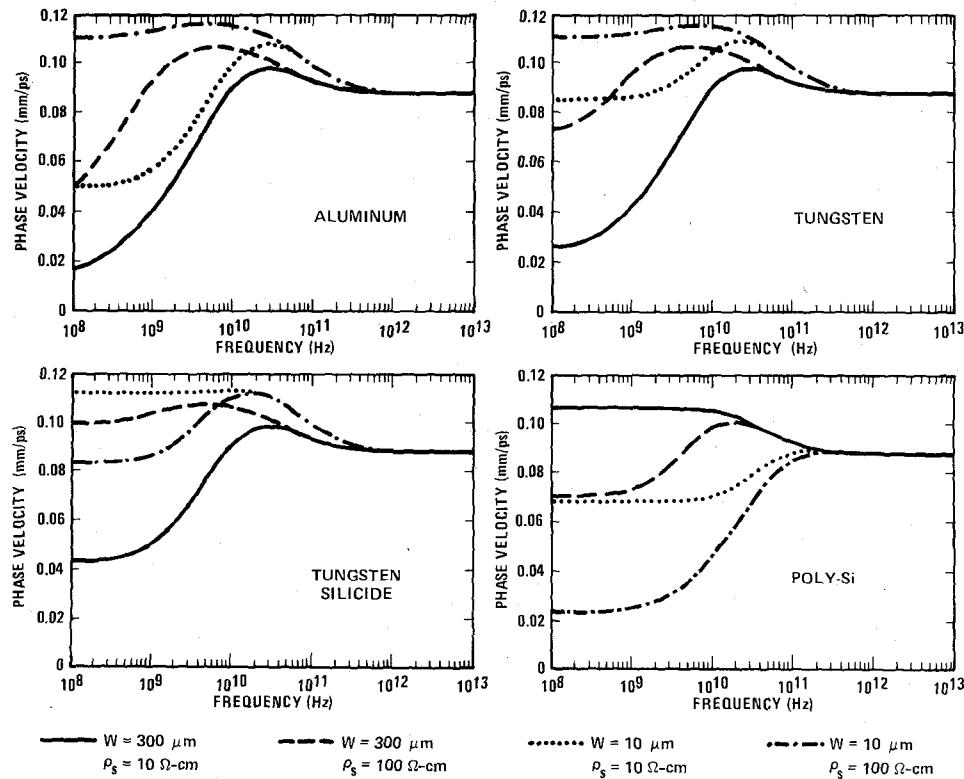

Fig. 7 shows the dependences of phase velocity on frequency for the same set of parameters as shown in Fig. 6. The most obvious consistency in the plots is that phase velocity in all cases reaches the high-frequency limiting velocity  $c/\sqrt{\epsilon_{\text{Si}}}$  and remains constant at frequencies above 500 GHz. This happens because  $\beta_0 \gg \alpha_c, \alpha_d$  for all the cases considered. However, this frequency range is outside the practical range of interest (below 100 GHz). Of more relevance is that all the 50  $\Omega$  lines show similar behavior down to 10 GHz: they show only geometric dispersion effects above this frequency. Below 10 GHz, the 50  $\Omega$  Al, W, and WSi<sub>2</sub> lines show a transition from a high-frequency quasi-TEM regime to a slower-phase-velocity low-frequency regime. This is reminiscent of but fundamentally different from the well-known non-quasi-TEM slow-wave regime first predicted by Guckel *et al.* [13] and elucidated by Hasegawa *et al.* [6]. For the quasi-TEM case considered here, low-frequency velocity increases as substrate resistivity increases. A rather interesting aspect of the results is that for the metal and silicide lines, on 10  $\Omega\cdot\text{cm}$  substrates, the low-frequency velocity *increases* as conductor resistivity *increases* and as line width *decreases*! Hasegawa *et al.* [6] first predicted this trend for changes in conductor line width, but ours is the first analysis that shows this

trend for changes in conductor resistivity. Finally, as expected from Fig. 5, geometric dispersion is greater for the 10  $\mu\text{m}$  lines than for the 300  $\mu\text{m}$  lines in Al, W, and WSi<sub>2</sub>.

The wider poly-Si lines are anomalous compared with the metal and silicide lines because lower phase velocity at low frequency occurs for the 100  $\Omega\cdot\text{cm}$  substrate but does not occur for the 10  $\Omega\cdot\text{cm}$  substrate. The narrow poly-Si lines are again anomalous compared with the metal and silicide lines in that they show reversed trends for low-frequency velocity compared with the wider lines. Finally, low-wave-velocity behavior extends to higher frequency for narrow poly-Si lines than for all the other cases considered. These anomalies for poly-Si lines can be explained by calculating the wave velocity for both  $\alpha_c$  and  $\alpha_d$  much greater than  $\beta_0$ . We may then write the phase velocity  $v$  as

$$v = \frac{v_0}{\sqrt{0.5 + 0.25(\alpha_c/\alpha_d + \alpha_d/\alpha_c)}}. \quad (18)$$

Here  $v_0$  is the phase velocity in the absence of losses. In this regime ( $\alpha_c, \alpha_d \gg \beta_0$ ), we can see that even though the net line loss is very high, if conductor and dielectric losses are comparable in magnitude, then wave velocity is *high*. If, however, one is much larger than the other, then wave velocity is *low*. The 300  $\mu\text{m}$  poly-Si lines on 10  $\Omega\cdot\text{cm}$  substrates have comparable substrate and conductor losses and thus show the maximum wave velocity  $v_0$ .

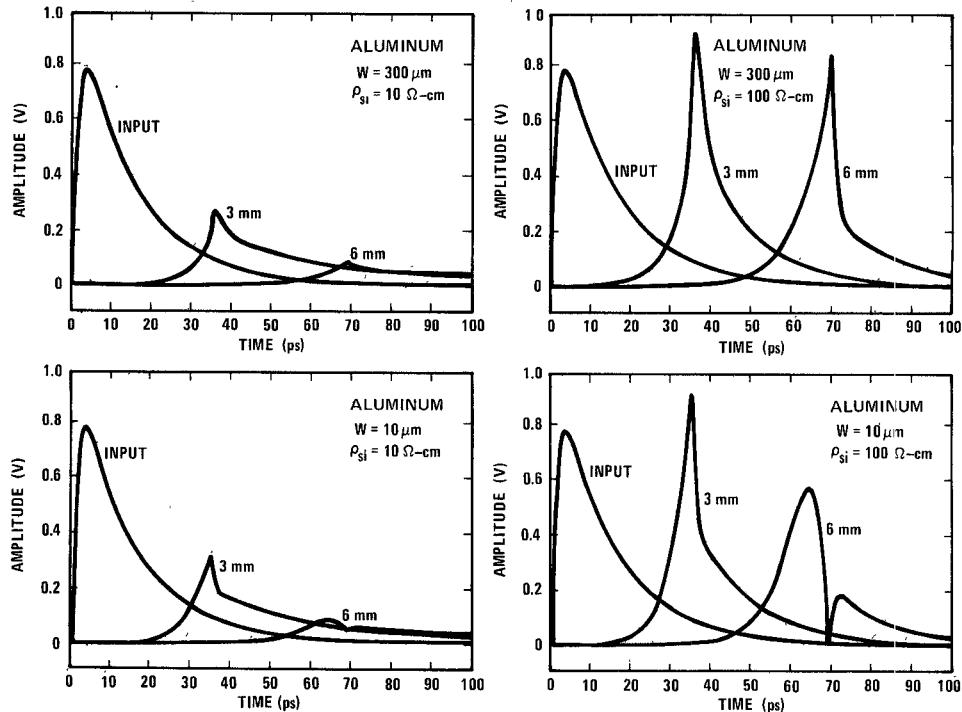

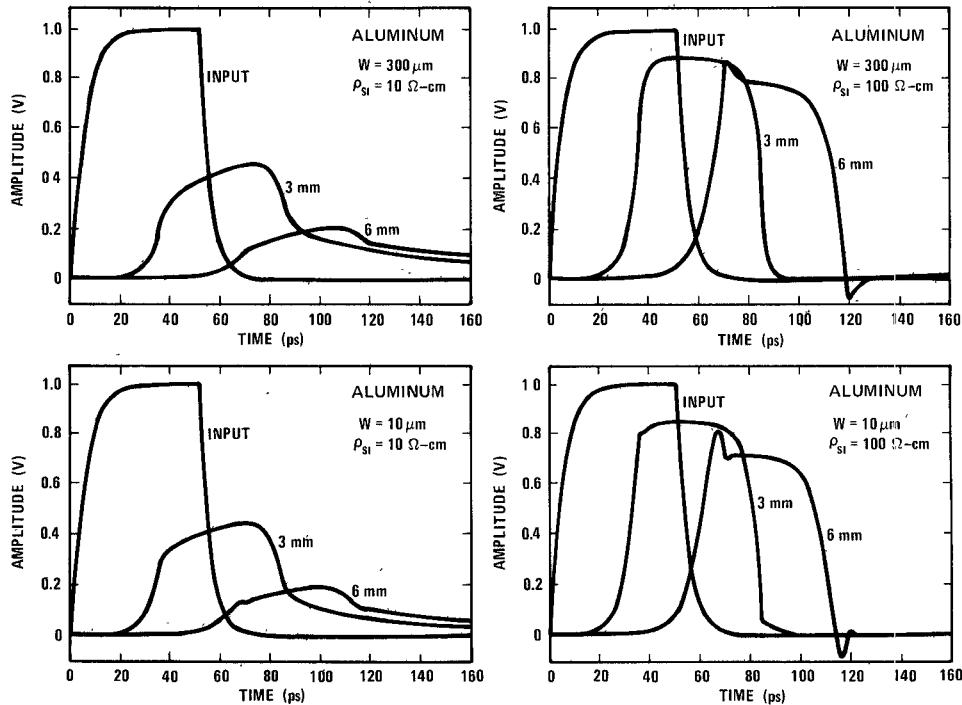

Figs. 8 and 9 show time-domain plots of exponential and square-wave pulses propagated for substrate resistivities of 10  $\Omega\cdot\text{cm}$  and 100  $\Omega\cdot\text{cm}$ , with Al interconnects. The parameters used for these plots are  $\tau_1 = 15$  ps and  $\tau_2 = 1$  ps for the exponential pulses; and  $\tau_1 = 50$  ps,  $\tau_2 = 5$  ps, and  $\omega_1 = 10^{12}$  Hz for the square-wave pulses. Fig. 8 shows the pulse-sharpening effect caused by geometric dispersion on asymmetric pulses noticed by Hasnain *et al.* [14]. Geometric dispersion appears in the square-wave pulses as an overshoot. For both exponential and square-wave pulses, geometric dispersion is a larger effect for the narrow line widths, as expected from Fig. 5.

Figs. 8 and 9 show that for a substrate resistivity of 10  $\Omega\cdot\text{cm}$ , the signal is severely attenuated by 6 mm, whereas for a substrate resistivity of 100  $\Omega\cdot\text{cm}$ , the signal is still recognizable at 6 mm. Since substrate resistivities of about 10  $\Omega\cdot\text{cm}$  are common in present integrated-circuit structures, signal attenuation on interconnections will become more of a problem as frequencies rise. Thus it is of great importance to use high-resistivity substrates when designing high-frequency microstrip interconnections for integrated circuits.

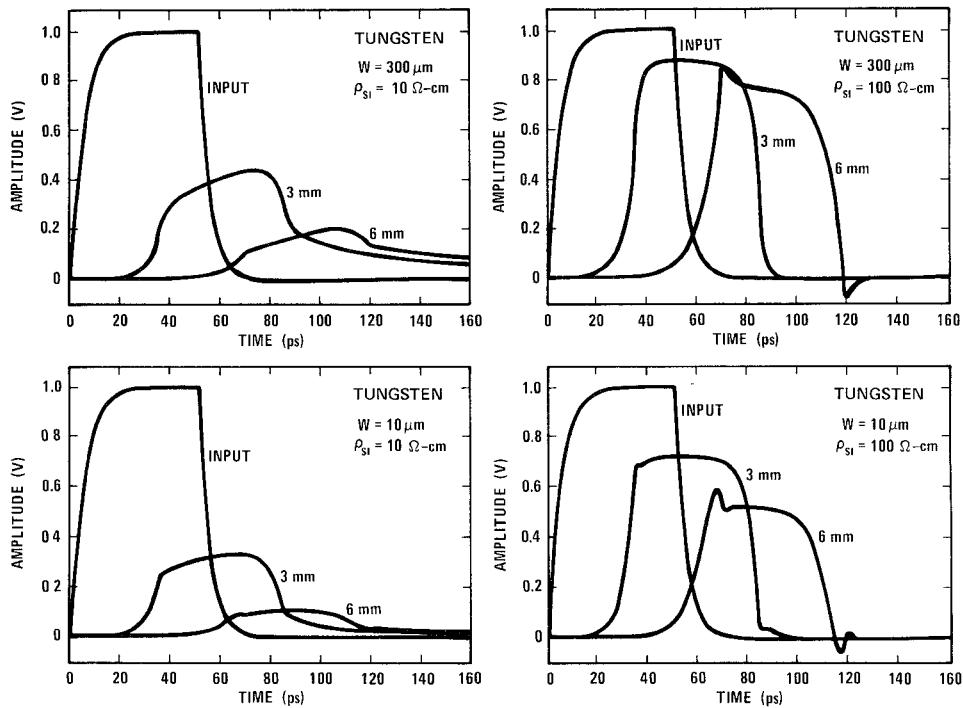

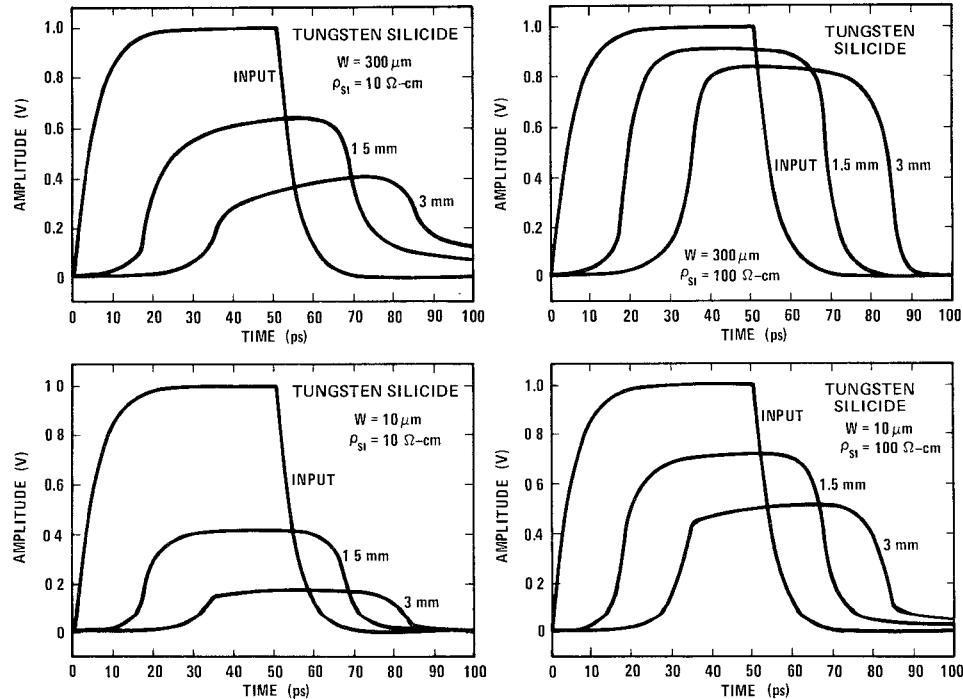

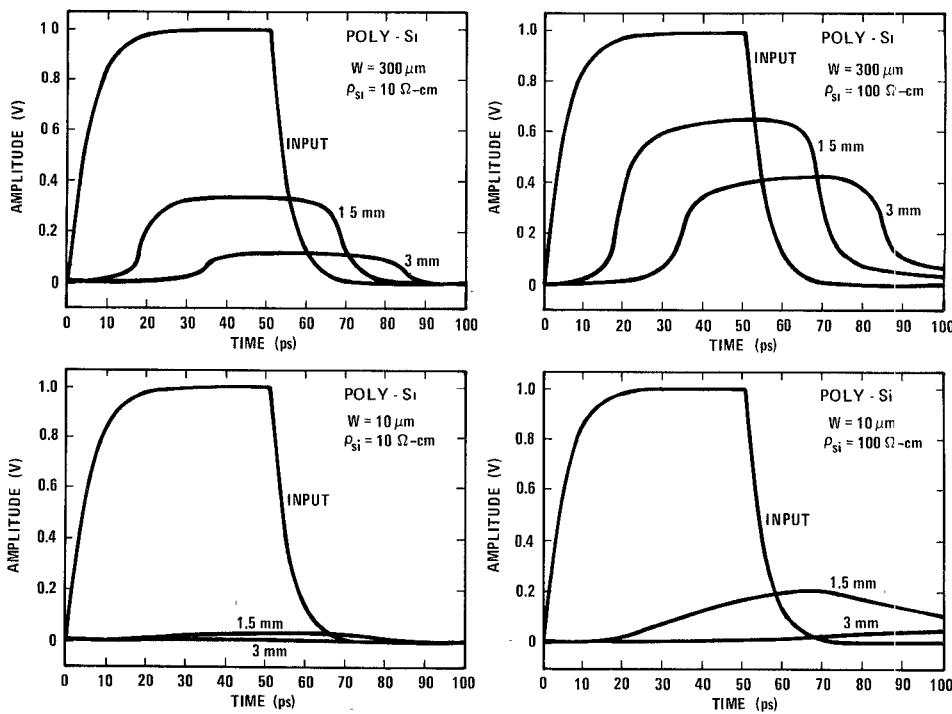

Figs. 10–12 show square-wave pulses propagated in W, WSi<sub>2</sub>, and poly-Si interconnections. W and WSi<sub>2</sub> lines show qualitatively similar results to those in Fig. 9 for Al interconnections: 10  $\Omega\cdot\text{cm}$  substrates show dramatic increases in loss compared with those of 100  $\Omega\cdot\text{cm}$  substrates. Conductor loss becomes increasingly significant from Al to W to WSi<sub>2</sub> lines, but the changes are not dramatic. Fig. 12 shows the very large losses for poly-Si lines for these very high speed pulses. Conductor losses are

Fig. 6. Plots of line loss  $\alpha$  versus frequency for Al ( $2.7 \mu\Omega \cdot \text{cm}$ ), W ( $10 \mu\Omega \cdot \text{cm}$ ),  $\text{WSi}_2$  ( $30 \mu\Omega \cdot \text{cm}$ ), and poly-Si ( $500 \mu\Omega \cdot \text{cm}$ ) microstrip lines on 450- $\mu\text{m}$ -thick Si wafers. Two substrate resistivities ( $10$  and  $100 \Omega \cdot \text{cm}$ ) and two conductor line widths ( $10$  and  $300 \mu\text{m}$ ) are considered. Conductor thickness is  $0.5 \mu\text{m}$ .

Fig. 7. Phase velocity versus frequency for Al ( $2.7 \mu\Omega \cdot \text{cm}$ ), W ( $10 \mu\Omega \cdot \text{cm}$ ),  $\text{WSi}_2$  ( $30 \mu\Omega \cdot \text{cm}$ ), and poly-Si ( $500 \mu\Omega \cdot \text{cm}$ ) microstrip lines on 450- $\mu\text{m}$ -thick Si wafers. Two substrate resistivities ( $10$  and  $100 \Omega \cdot \text{cm}$ ) and two conductor line widths  $10$  and  $300 \mu\text{m}$ , are considered. Conductor thickness is  $0.5 \mu\text{m}$ .

Fig. 8. Exponential pulses after 0, 3, and 6 mm of propagation on Al microstrip lines on 450- $\mu\text{m}$ -thick Si wafers. Two substrate resistivities ( $10$  and  $100$   $\Omega\cdot\text{cm}$ ) and two conductor line widths ( $10$  and  $300$   $\mu\text{m}$ ) are considered. The input pulses have 10 percent to 90 percent rise times of  $2.2$  ps and fall times of  $33$  ps. Aluminum thickness is  $0.5$   $\mu\text{m}$  and resistivity is  $2.7$   $\mu\Omega\cdot\text{cm}$ .

Fig. 9. Square-wave pulses after 0, 3, and 6 mm of propagation on Al microstrip lines on 450- $\mu\text{m}$ -thick Si wafers. Two substrate resistivities ( $10$  and  $100$   $\Omega\cdot\text{cm}$ ) and two conductor line widths ( $10$  and  $300$   $\mu\text{m}$ ) are considered. The input pulses have 10 percent to 90 percent rise times and fall times of  $12$  ps, and  $50$  ps pulse lengths. Aluminum thickness is  $0.5$   $\mu\text{m}$  and resistivity is  $2.7$   $\mu\Omega\cdot\text{cm}$ .

Fig. 10. Square-wave pulses after 0, 3, and 6 mm of propagation on W microstrip lines on 450- $\mu\text{m}$ -thick Si wafers. Two substrate resistivities (10 and 100  $\Omega\cdot\text{cm}$ ) and two conductor line widths (10 and 300  $\mu\text{m}$ ) are considered. The input pulses have 10 percent to 90 percent rise times and fall times of 12 ps, and 50 ps pulse lengths. Tungsten thickness is 0.5  $\mu\text{m}$  and resistivity is 10  $\mu\Omega\cdot\text{cm}$ .

Fig. 11. Square-wave pulses after 0, 1.5, and 3 mm of propagation on  $\text{WSi}_2$  microstrip lines on 450- $\mu\text{m}$ -thick Si wafers. Two substrate resistivities (10 and 100  $\Omega\cdot\text{cm}$ ) and two conductor line widths (10 and 300  $\mu\text{m}$ ) are considered. The input pulses have 10 percent to 90 percent rise times and fall times of 12 ps, and 50 ps pulse lengths. Tungsten silicide thickness is 0.5  $\mu\text{m}$  and resistivity is 30  $\mu\Omega\cdot\text{cm}$ .

Fig. 12. Square-wave pulses after 0, 1.5, and 3 mm of propagation on poly-Si microstrip lines on 450- $\mu$ m-thick Si wafers. Two substrate resistivities (10 and 100  $\Omega\cdot\text{cm}$ ) and two conductor line widths (10 and 300  $\mu\text{m}$ ) are considered. The input pulses have 10 percent to 90 percent rise times and fall times of 12 ps, and 50 ps pulse lengths. Polycrystalline silicon thickness is 0.5  $\mu\text{m}$  and resistivity is 500  $\mu\Omega\cdot\text{cm}$ .

extremely high but significant improvement is achieved by going to 100  $\Omega\cdot\text{cm}$  substrates, just as in the cases with the other lines. However, it is clear that poly-Si interconnections will only be useful for short line lengths on future high-performance Si VLSI circuits.

## V. CONCLUSIONS

For conductor line widths as narrow as 10  $\mu\text{m}$ , we have shown that substrate losses dominate over conductor losses for Al, W, and WSi<sub>2</sub> microstrip interconnections on Si IC substrates at 100 MHz to 100 GHz frequencies. For the cases we considered, conductor losses were dominant only for narrow poly-Si lines. The use of very narrow (1  $\mu\text{m}$ ) line widths will probably only slightly alter this simple picture. These results imply that future improved-performance Si VLSI circuits will require higher resistivity substrates than are now used. However, W and WSi<sub>2</sub> lines will provide high-performance interconnections, which will be useful for these circuits, even with relatively narrow line widths.

We have seen that the lowering of phase velocity at low frequencies is negated as conductor line widths decrease and as conductor resistivity increases for Al, W, and WSi<sub>2</sub> lines. These results show that as conductor dimensions are decreased and the resulting higher current densities require W and WSi<sub>2</sub> lines for reduced electromigration, this effect may be virtually eliminated for very high speed VLSI.

We have shown the surprising result that for poly-Si lines, wave-velocity lowering at low frequency does *not* occur on Si IC's when conductor and substrate losses are both high but comparable in magnitude. In practice, this

means that for short line lengths where high loss can be tolerated, poly-Si or other high-resistance lines may achieve shorter interconnection delays than low-resistance lines!

We have shown that geometric dispersion in microstrip will affect pulse propagation for switching speeds  $< 35$  ps. Also, the magnitude of the geometric dispersion effects will increase as conductor line widths are narrowed. These results are also valid for pulse propagation in microstrip lines on other IC substrates, e.g., Si on sapphire, GaAs, and InP, because these substrates have very similar dielectric constants to that of Si. It is significant for applications that these other substrates can have much higher resistivities than silicon and thus not suffer from dielectric loss.

## REFERENCES

- [1] P. M. Solomon, "A comparison of semiconductor devices for high-speed logic," *Proc. IEEE*, vol. 70, pp. 489-509, 1982.

- [2] D. L. Fraser, Jr., H. J. Boll, R. J. Bayrums, N. C. Wittner, and E. N. Fuls, "Gigabit logic circuits with scaled NMOS," in *ESSCIRC 1981, Dig. Tech. Papers*, pp. 202-204.

- [3] S. Konaka, Y. Yamamoto, and T. Sakai, "A 30-ps Si bipolar IC using super self-aligned process technology," *IEEE Trans. Electron Devices*, vol. ED-33, pp. 526-531, 1986.

- [4] H. Hasegawa and S. Seki, "On-chip pulse transmission in very high speed LSI/VLSI," in *IEEE Microwave and Millimeter-Wave Monolithic Circuits Symp. Dig.* (San Francisco), 1984, pp. 29-33.

- [5] D. G. Corr and J. B. Davies, "Computer analysis of the fundamental and higher order modes in single and coupled microstrip," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-20, pp. 669-678, 1972.

- [6] H. Hasegawa, M. Furukawa, and H. Yanai, "Properties of microstrip line on Si-SiO<sub>2</sub> system," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-19, p. 869, 1971.

- [7] W. R. Eisenstadt, R. B. Hammond, and R. W. Dutton, "Integrated silicon photoconductors for picosecond pulsing and gating," *IEEE Electron Device Lett.*, vol. EDL-5, pp. 296-299, 1984.

- [8] M. V. Schneider, "Microstrip lines for microwave integrated circuits," *Bell Syst. Tech. J.*, vol. 48, p. 1421, 1969.

- [9] K. C. Gupta, R. Garg, and R. Chadha, *Computer-Aided Design of Microwave Circuits*. Dedham, MA: Artech House, 1981, p. 62.

- [10] E. Yamashita, K. Atsuki, and T. Ueda, "An approximate dispersion formula of microstrip lines for computer-aided design of microwave integrated circuits," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-27, p. 1036, 1979.

- [11] R. A. Pucel, D. J. Masse, and C. P. Hartwig, "Losses in microstrip," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-16, p. 342, 1968.

- [12] J. D. Welch and H. J. Pratt, "Losses in microstrip transmission systems for integrated microwave circuits," in *NEREM Rec.*, vol. 8, 1966, p. 100.

- [13] H. Guckel, P. A. Brennan, and I. Palocz, "A parallel plate waveguide approach to microminiaturized planar transmission lines for integrated circuits," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-15, pp. 468-476, 1967.

- [14] G. Hasnain, G. Arjavalangam, A. Dienes, and J. R. Whinnery, "Dispersion of picosecond pulses on microstrip transmission lines," in *Proc. Conf. Picosecond Optoelectronics* (San Diego), 1983, pp. 159-163.

\*

In 1988, he joined AT&T Bell Laboratories, Holmdel, NJ. His work is in optoelectronic device physics and technology.

Dr. Goossen has authored several papers, and is a member of the American Physical Society.

\*

**Robert B. Hammond** (M'79) received the B.S. degree in physics, the M.S. degree in applied physics, and the Ph.D. degree in applied physics from the California Institute of Technology in 1971, 1972, and 1975, respectively. Since 1973 his professional work has been involved primarily with experimental and theoretical studies in semiconductor physics and semiconductor device physics.

In August 1975 he joined the technical staff of the Air Force Weapons Laboratory, where he worked on developing a chemically pumped iodine laser. In October 1976 he joined the Electronics Division of the Los Alamos National Laboratory as a staff member. In 1985, he became Deputy Group Leader for Electronics Research there and directed a group of researchers in semiconductor physics, materials, and devices. His research at Los Alamos included studies of excitons and electron-hole liquid in Si, the development of optical devices for CO<sub>2</sub> lasers, pulsed laser annealing of Si, ultrafast photoconductive detectors and switches, and single-event upset in semiconductor devices. In December 1987 he joined Superconductor Technologies Inc., Santa Barbara, CA, where he is involved in developing thin-film high-temperature superconductors for microelectronic applications.

Dr. Hammond has coauthored more than 60 technical papers published in refereed conference proceedings and journals. He is a member of the American Physical Society, the Materials Research Society, and the Bohmische Physical Society.

**Keith W. Goossen** (M'88) was born in Kingsburg, CA, in 1961. He received the B.S. degree in electrical engineering from the University of California, Santa Barbara, in 1983 and the Ph.D. degree in electrical engineering from Princeton University, Princeton, NJ, in 1988.